These slides are based on Digital Fundamentals 9th ed. Karnaugh maps for present-state J and K inputs.Įxample: Designing a counter with the irregular binary sequence 1-> 2 -> 5 -> 7 We work this example entirely on the black board. Next-State Table Examples of the mapping procedure for the counter sequence represented. State Diagram State diagram for a 3-bit Gray code counter. All sequential circuits have excitation variables and state variables.ĭesign Procedure for Sequential Circuits as Applied to Counters.

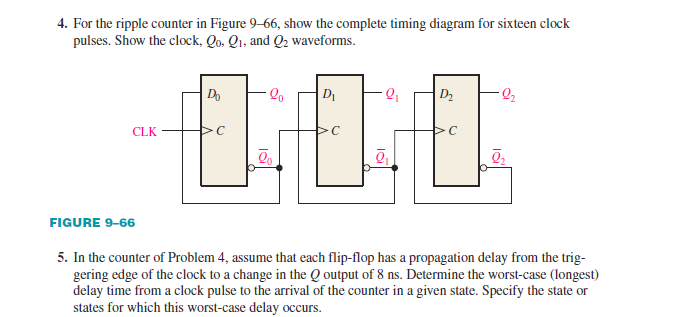

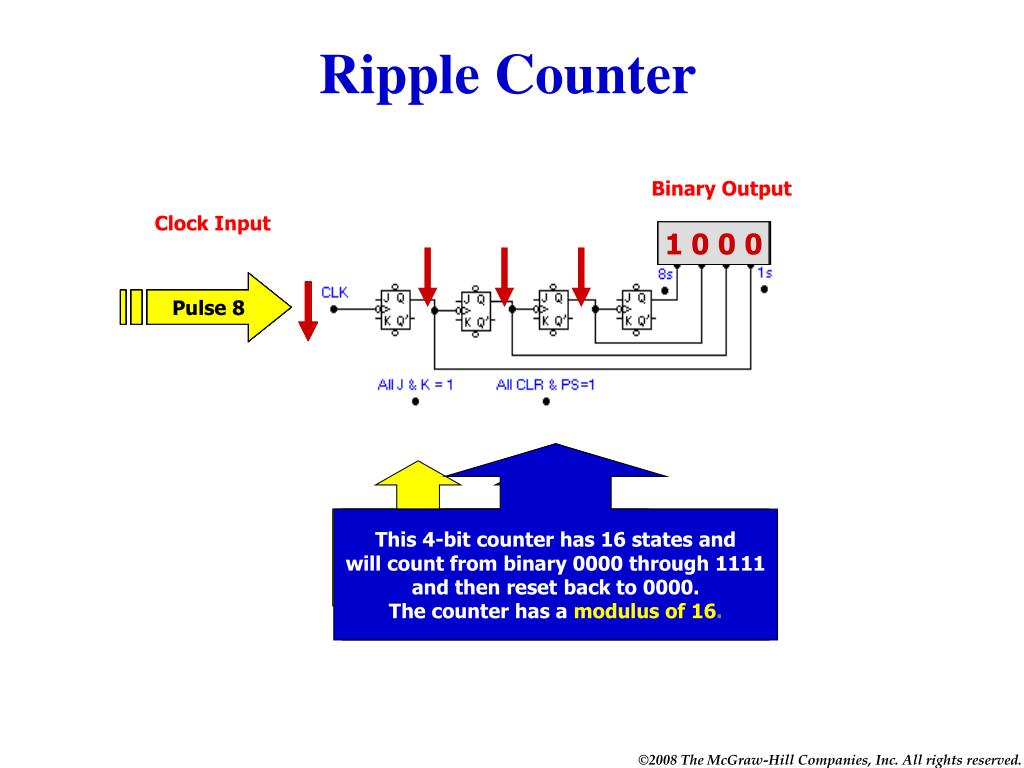

Not all sequential circuits are required to have inputs and outputs.The information in the memory and the inputs to them combinational logic are required for the operation of the circuit.A sequential circuit (state machine) consists of a combinational logic section and a memory section (flip-flops).Q1♽OWNĪ basic 3-bit up/down synchronous counter.We study 3-bit up/down synchronous counterģ-bit up/down synchronous counter J0 = K0 = 1 J1 = K1 = Q0.It is capable of progressing in either direction up or down in a certain sequence.Timing diagram for the BCD decade counter (Q0 is the LSB). Timing details for the 2-bit synchronous counter operation (the propagation delays of both flip-flops are assumed to be equal). Timing diagram for the 2-bit synchronous counter. The J and K inputs of FF1 are having 00 or 11 depending on Q0.Both flip-flops are triggered by the clock.Īn asynchronously clocked decade counter with asynchronous recycling. Two unique states (in this case) are sufficient to decode the count of ten.2.2 Draw a timing diagram for a n-bit ripple counter ( n <. connecting the output of the NAND gate to the clear inputs of the flip-flops. 2.1 Draw a schematic diagram of a n-bit ripple counter ( n This is done as shown in the next slide by decoding count 1010 with an NAND gate and.The BCD decade counter is recycled to 0000 after the 1001 state.Sketch the timing diagram for a 4-bit ripple counter which. Since the counter would have 16 states, it is forces to recycle before going through all of its possible state. Electrical Engineering Assignment Help, Sketch the timing diagram for a 4-bit ripple counter, Q.A decade counter of states from 0000 to 1001 is called a BCD decade counter.These counters have 10 states in their sequence.FF3 is triggered by the Q2 output of FF2 at the positive going transition.įour-bit asynchronous binary counter and its timing diagram.FF2 is triggered by the Q1 output of FF1 at the positive going transition.FF2 is triggered by the Q1 output of FF1 at the positive going transition.ģ-bit asynchronous binary counter and its timing diagram for one cycle.FF1 is triggered by the Q0 output of FF0 at the positive going transition.FF0 is triggered by the clock at the positive going edge of.Baraka Logic Design (CSCI 2301) Department of Computer Science Faculty of Information Technology The Islamic University of Gaza For T Flipflop when input=0, Output=1.For D Flipflop when input=0, Output=0. From the above timing diagram, it is clear that the state of the second flip flop is changed when the output Q 0 goes transition from 1 to 0.For J-K flip-flop, if J=K=1, and if clk=1 for a long period of time, then output Q will toggle as long as CLK remains high which makes the output unstable or uncertain.This makes the Master-Slave J-K flip flop a Synchronous device which passes data with the clock signal.Toggling takes place during the whole process since the output changes once in a cycle.When the clock is low, the slave becomes operational and remains high until the clock again becomes low.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed